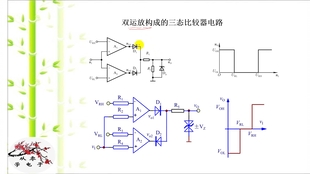

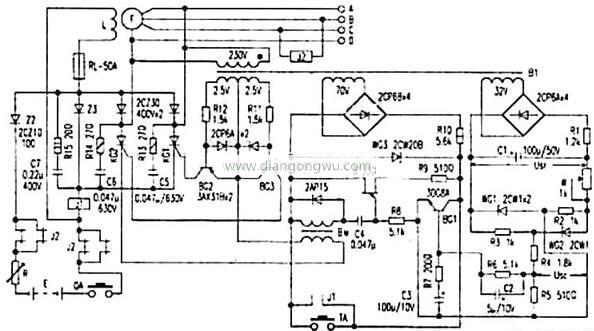

電源回路の基礎知識(1) また、スイッチング・レギュレータと比較して基本的に低コストで実装できます。 図2 リニア・レギュレータの動作の原理 可変抵抗と負荷抵抗によって分圧回路が構成され、分圧された電圧が負荷に供給される。コンパレータ(比較器)」で実験したものを使います。一方、三角波についてですが、思い出して頂きたいのが前章で学習した矩形波(方形波)発生回路です。矩形波発生回路の回路図を図4 (a) に示していますが、B点の電圧は同図 (b) のような波形です。アナログ技術シリーズ アナログ集積回路 Ⓒ05 Gunma Industry Support Organization 15 従来型AD変換器(逐次比較型)原理図 前置フィルタ 荒い特性の フィルタ 高精度 フィルタ 信号帯域 fн/2 fs/2 fн/2 fн fs 比較器 DA変換器 逐次比較 レジスタ デジタル 信号処理

Tq 100型同期继电器 上海约瑟电器有限公司

比較回路 ヒステリシス

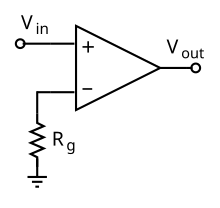

比較回路 ヒステリシス-多ビット比較器の場合 比較器のビット数と出力の組み合わせ数 1 1ビット 21×21= 4通り 2 2ビット 22×22= 16通り 3 3ビット 23×23= 64通り 4 4ビット 24×24= 256通り ビット数が増えるにつれ膨大な組み合わせが必要オペアンプ(operational amplifier,オペレーショナル・アンプリファイア)は、非反転入力端子()と反転入力端子()と、一つの出力端子を備えた増幅器の電子回路モジュールである 。 日本語では演算増幅器という 。 OPアンプなどと書かれることもある 。 増幅回路、コンパレータ、積分回路

請教 單切 三切開關 Mobile01

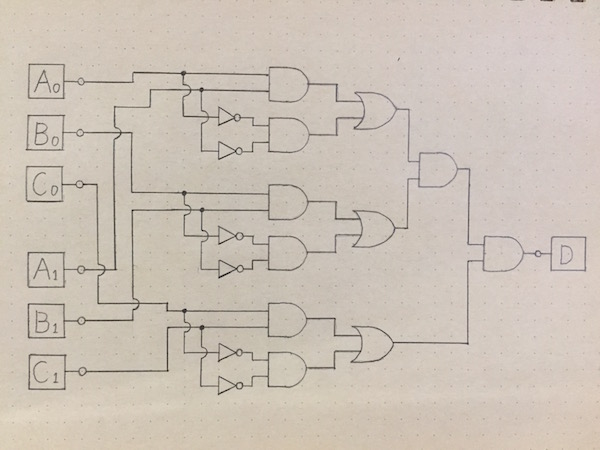

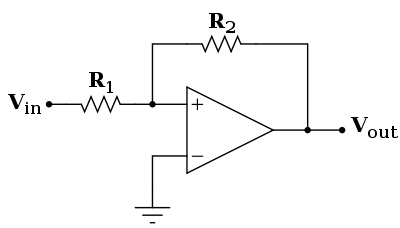

1 ビット比較器を利用して次に複数ビット比較器を実現する。例として 2 ビット比較器を取り上げる。 この回路は入力された 2 ビットの2進数 a1,a0 と b1,b0 の大小関係を判定する。 a1, b1 が上位桁になる。真理値表は次のようになる。電子回路 コンパレータ(比較器とも言う)は、2つの電圧を比較するために用いられます。 オペアンプを用いてコンパレータ(比較器)を実現します。 電子回路設計 入門サイト 電子回路設計 入門サイト トップページ サイトマップ&What's new!信号の演算(比較) 2つの電圧の大小を比較するには 比較回路(comparator)を用いる。比 較回路は負帰還をかけない回路を 用いるため、入力端子間のわずか な電位差で出力電圧が飽和する。 そこで、反転入力端子に基準電圧V r、 非反転入力端子に信号電圧V

2 組合せ回路の設計 加算器(1) 2進法 桁上げ 28) 11 17 10進法 通常の 代数 11=10 ) 011=10比較回路というのは2つの入力信号が同じであれば「1」を出力する回路のことで、これも「 NOT 回路」「 OR 回路」「 AND 回路」の組合せで作ることができます。 構造は以下のようになっています。 端子A0、B0、C0から入力された信号と端子A1、B1、C1から入力された信号に対して、それぞれA0とA1、B0とB1、C0とC1が同じであるかどうかを「 AND 回路」を使って調べていますこの出力電圧 V o とアナログ入力電圧 V i とが比較回路で比較され、制御回路にフィードバックされる。 第2図 逐次比較形A/D変換器の原理 制御回路は、

比較器,エンコーダ及びデコーダをロジックトレーナ上に構成し,その動作を確認する. 2. 演習 (1) 各論理回路の真理値表を書く. (2) 真理値表から特殊加法標準形などを用いて,論理関数を導出する. (3) 必要に応じてド・モルガンの定理を用いて,論理コンパレータ(比較器)」で実験したものを使います。一方、三角波についてですが、思い出して頂きたいのが前章で学習した矩形波(方形波)発生回路です。矩形波発生回路の回路図を図4 (a) に示していますが、B点の電圧は同図 (b) のような波形です。電源回路の基礎知識(1) また、スイッチング・レギュレータと比較して基本的に低コストで実装できます。 図2 リニア・レギュレータの動作の原理 可変抵抗と負荷抵抗によって分圧回路が構成され、分圧された電圧が負荷に供給される。

电流信号在控制回路中的作用 大大通

板級電源設計之ldo晶片選型及電路設計 每日頭條

複雑な回路をより簡単な回路(設計済み)の 組み合わせで作る –設計が簡単になる –回路の量産化で製作コスト削減 回路のモジュール化 • 回路全体を1つのゲートとみなす 例 比較器 Zeq X Y ZX ZY Comp Comp Zeq X Y ZX ZY モジュール化 大小比較 3桁の数の大小比較複雑な回路をより簡単な回路(設計済み)の 組み合わせで作る –設計が簡単になる –回路の量産化で製作コスト削減 回路のモジュール化 • 回路全体を1つのゲートとみなす 例 比較器 Zeq X Y ZX ZY Comp Comp Zeq X Y ZX ZY モジュール化 大小比較 3桁の数の大小比較多ビット比較器の場合 比較器のビット数と出力の組み合わせ数 1 1ビット 21×21= 4通り 2 2ビット 22×22= 16通り 3 3ビット 23×23= 64通り 4 4ビット 24×24= 256通り ビット数が増えるにつれ膨大な組み合わせが必要

コンパレータ 比較器

運算放大器 比較器的電路結構 電子小百科 Electronics Trivia 羅姆半導體集團 Rohm Semiconductor

複雑な回路をより簡単な回路(設計済み)の 組み合わせで作る –設計が簡単になる –回路の量産化で製作コスト削減 回路のモジュール化 • 回路全体を1つのゲートとみなす 例 比較器 Zeq X Y ZX ZY Comp Comp Zeq X Y ZX ZY モジュール化 大小比較 3桁の数の大小比較あらまし 2つの信号間の位相差に応じた電圧を出力する 位相比較器 は、現在では 位相周波数比較器 (Phase Frequency Comparator) と 呼ばれている回路方式の デジタル型比較器が多く用いられている。 この方式の 位相比較器 は、1サイクル以内の比較は 位相比較 を行い 誤差と比例した制御電圧を発生オペアンプ 回路構成 オペアンプは一般的に入力段、利得段、出力段の3段階内部回路構成となっています。 入力段は差動増幅段で構成されており、2つの端子間の差電圧を増幅します。 次に、入力段の差動増幅回路のみでは利得が不十分であるため、利得段によりさらにオペアンプの開放利得

过流自锁电路 Eda365电子论坛通信数码 人工智能 计算机 半导体 手机家电消费电子硬件门户网站

长模组上的采样回路阻抗 电阻

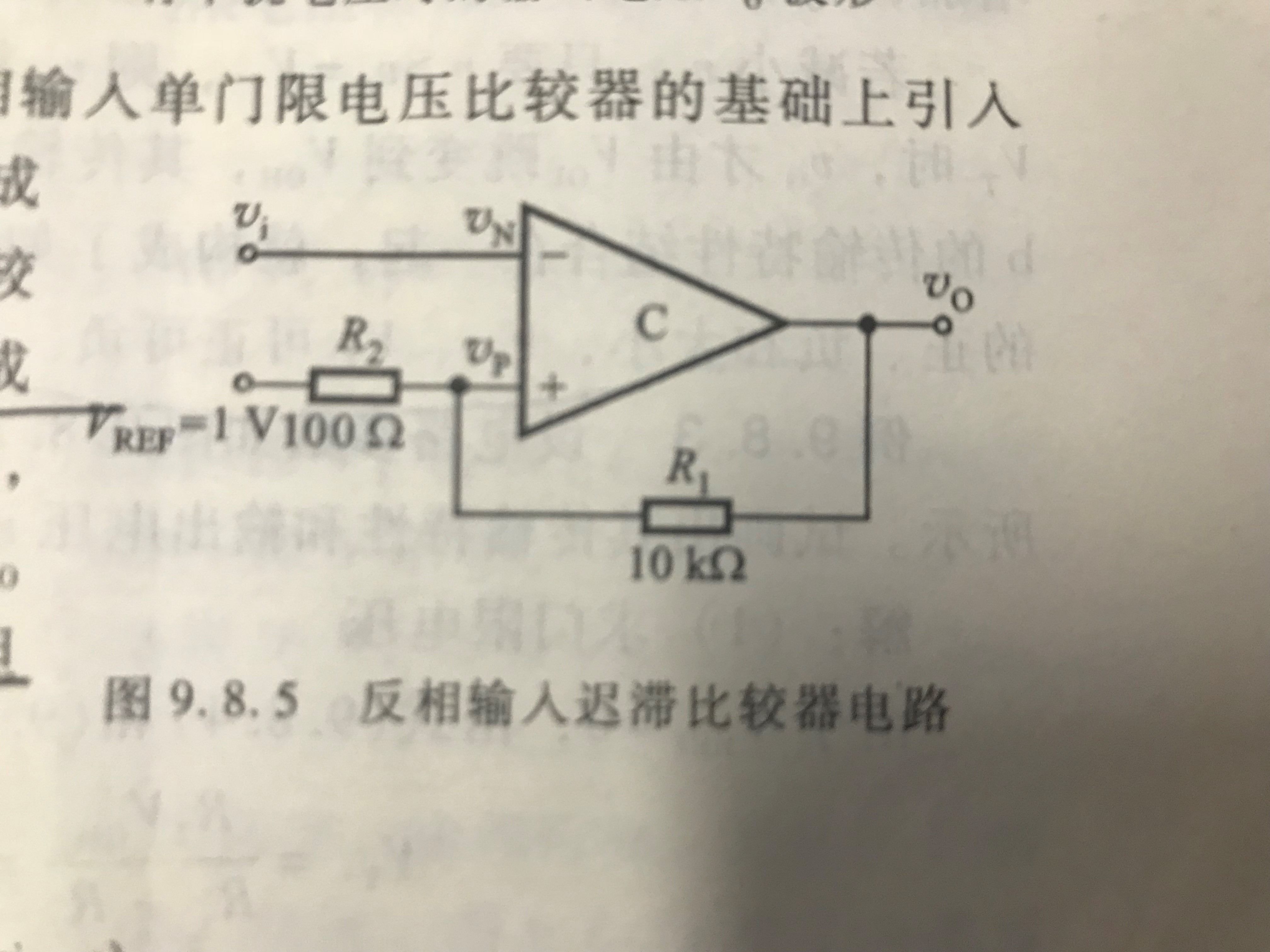

ハミング比較回路と同様の比較方法で、それぞれ、2つのデジタル数間の以上、以下、同等という比較結果が得られる。 図面の簡単な説明 0025 図1本発明のハミング比較回路の回路構成図である。 図2分圧回路の動作結果。この回路は、シュミット回路とか、ヒステリシス回路とも呼ばれています。 基本的な回路構成は下図のようにし、基準電圧Etが比較の基準になり ます。 この回路では、出力電圧のR2とR3による分圧した電圧がヒステリシスと三菱電機製シーケンサfxシリーズにおける「比較」命令とは、 2つの定数やデバイスの値を比較して、大・一致・小の3パターンをビットデバイスに出力する ラダープログラム命令です。 比較命令を用いることにより、2つの定数やデバイスの値の大小の状態により出力・処理内容を変更すること

トランジスタによる帰還増幅型定電圧電源回路

コンパレータ 比較器 電子工作で覚える 電子回路

応用2:比較回路 大きさの比較回路(1ビット) 2進数の大きさを比較する回路を作成します。まず、一桁の比較回路を考えます。a と bを比較し、aがbより小さいときl、等しいときe、大きいとき g、を1とします。 e=a・b は間違いです。比較回路 比較回路 (コンパレータ)は、入力された数値を比較して、一致や大小を判定する回路です。 図1は、2つの2ビットの入力信号A,Bを比較する回路のシンボル図です。 表1は、図1の比較回路の真理値表です。 入力Aは2ビットで、下位ビットをA 0で表し、上位ビットをA 1で表します。 同様に、入力Bは2ビットで、下位ビットをB 0で表し、上位ビットをB 1で比較器,エンコーダ及びデコーダをロジックトレーナ上に構成し,その動作を確認する. 2. 演習 (1) 各論理回路の真理値表を書く. (2) 真理値表から特殊加法標準形などを用いて,論理関数を導出する. (3) 必要に応じてド・モルガンの定理を用いて,論理

将运算放大器用作比较器时需要注意的事项 电子发烧友网

对比较器的使用方法的研究 Amoreentern的博客 Csdn博客

Woa1 位相比較器 pll回路およびdll回路 Google Patents

比較回路 コンピュータの仕組み 研究開発 相楽製作所

5 ビットコンパレータ回路

过流自锁电路 Eda365电子论坛通信数码 人工智能 计算机 半导体 手机家电消费电子硬件门户网站

独立回路电压方程个数 三人行教育网 Www 3rxing Org

4 組合せ回路 Digital Electronic Circuits 1 0 ドキュメント

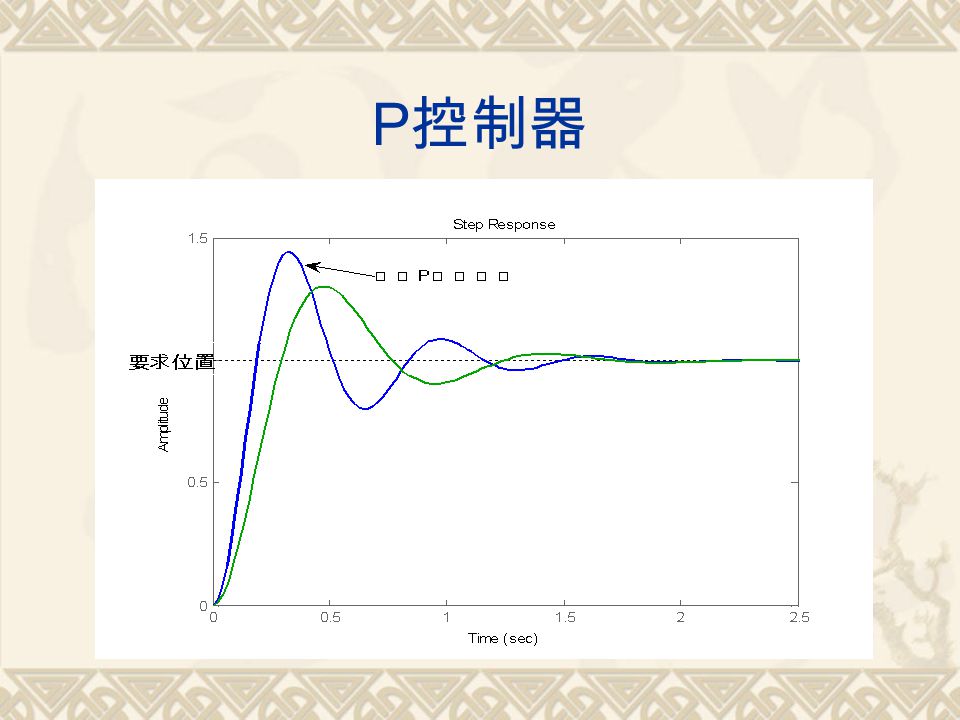

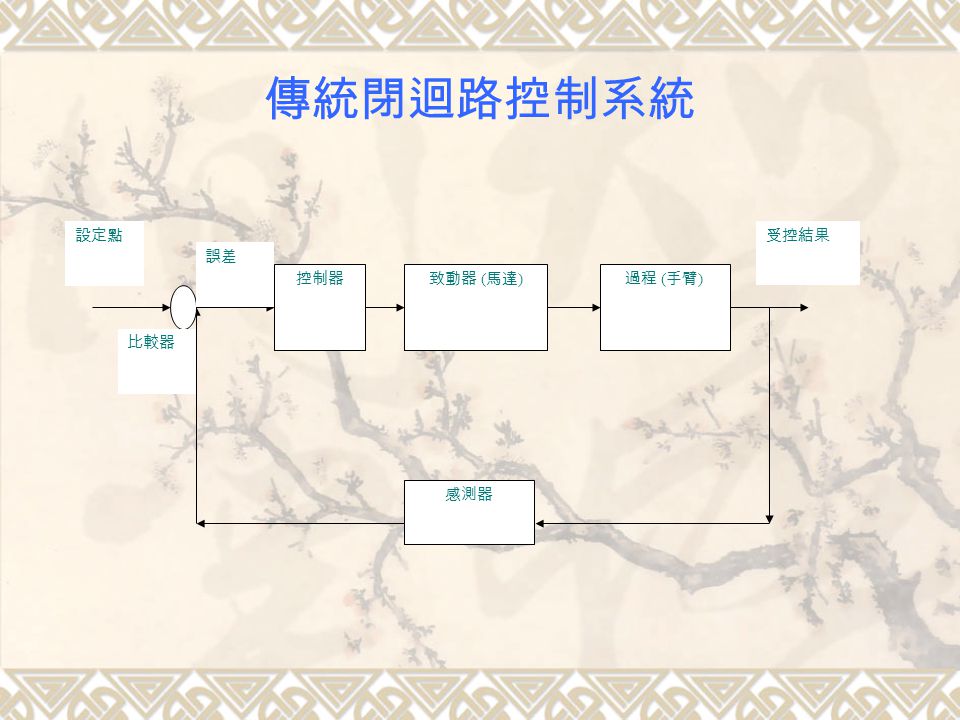

傳統閉迴路控制系統控制器致動器 馬達 過程 手臂 感測器設定點受控結果誤差比較器 Ppt Katebasma

实例分析 四个方面谈llc变压器设计经验 面包板社区

電子迴路 Wikiwand

插座迴路連接工法有哪些 怎麼接比較安全 立宇生活科技

频率跟踪式电动汽车无线充电系统的研究 杂志论文 电子产品世界

位相比較器 Phase Frequency Comparator の動作

继电保护及二次回路 国网教材 电流

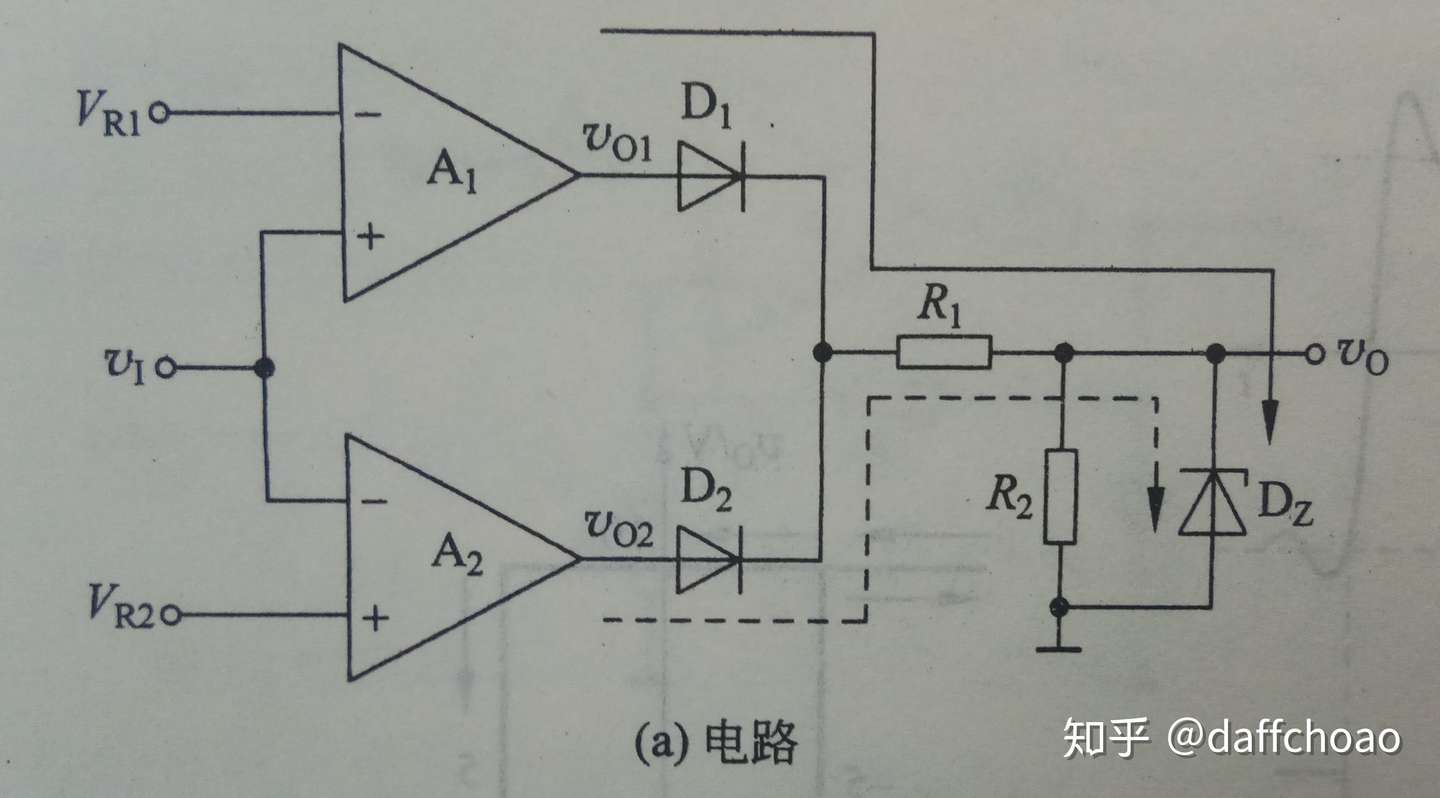

窗口比较电路的工作原理是什么 有什么用途 与滞回比较器的区别是什么 哔哩哔哩 つロ干杯 Bilibili

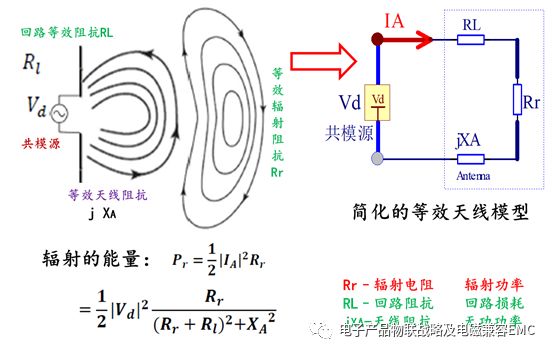

功率电子pfc系统的emi分析与设计 维科号

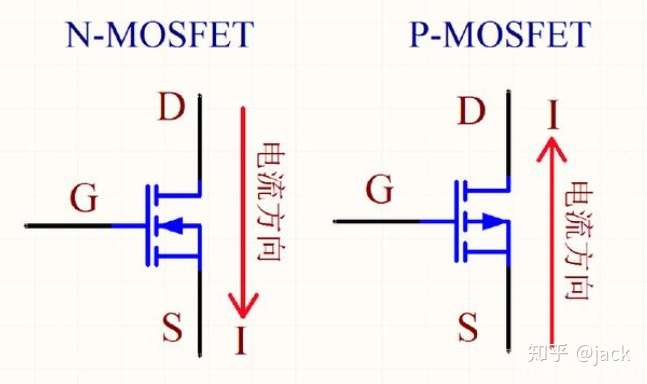

Mos管当开关控制时 一般用pmos做上管nmos做下管 知乎

运放的应用 续 滤波电路与电压比较器 知乎

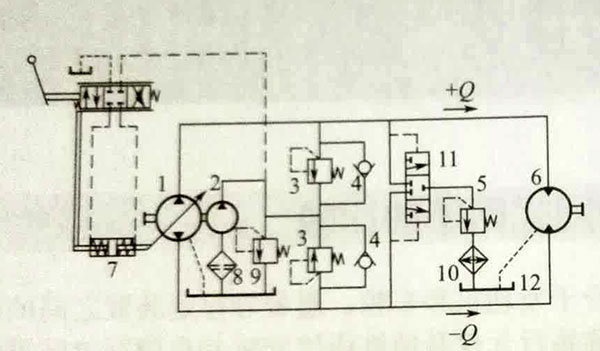

5 5 2快速运动回路 哔哩哔哩 つロ干杯 Bilibili

コンパレータ 比較器

Woa1 逐次比較型ad変換回路 Google Patents

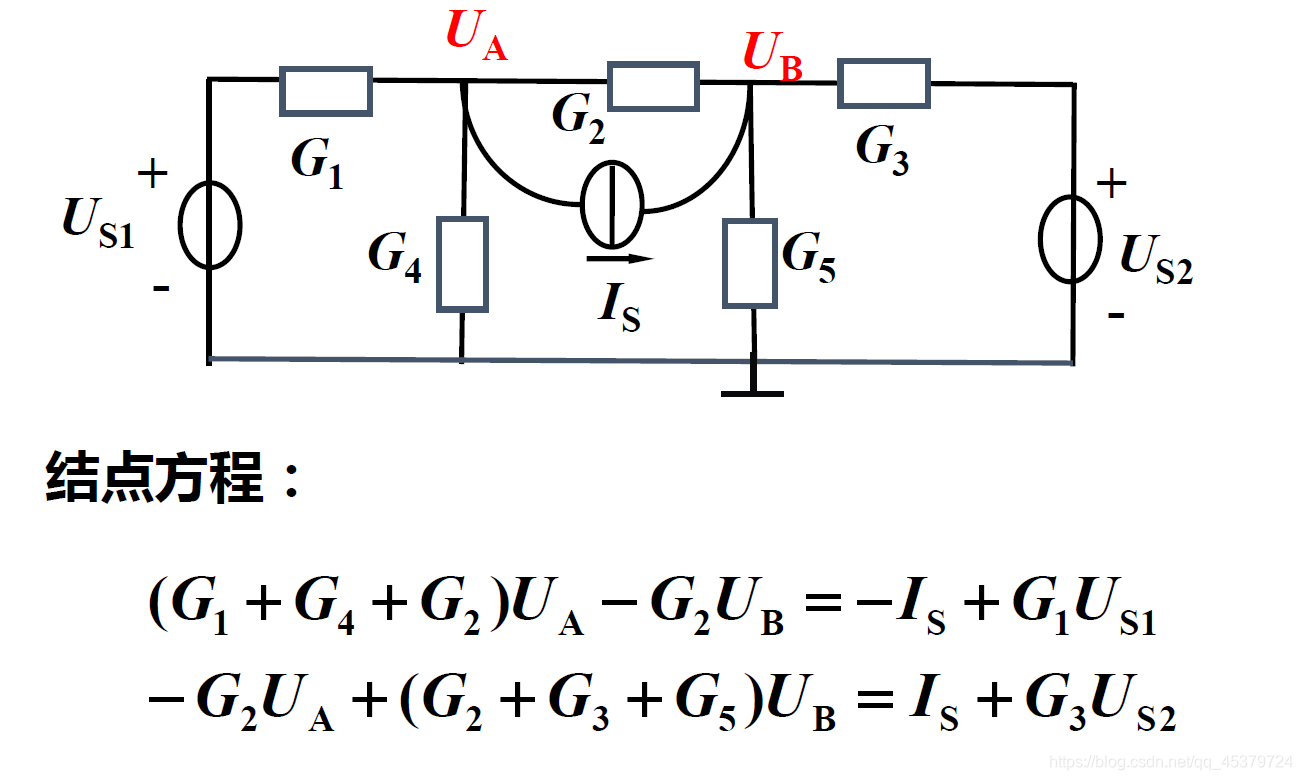

电路circuit Chapter3 Methods Of Analysis Oasis的博客 Csdn博客

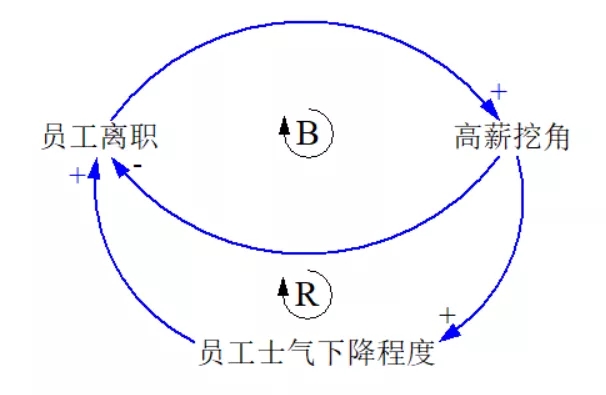

一文搞懂因果回路图 掌握系统思考关键工具 管理人网 中国第一企业管理资源中心

請教 單切 三切開關 Mobile01

悟空问答 在数控系统中开环与闭环 半闭环 系统的区别 1个回答

运算放大器 维基百科 自由的百科全书

コンパレータとは何か 回路の基本とコンパレータ回路の設計方法を勉強しよう ポイントはこれだ 比較 の原理 切り替わり動作 コンパレータ使用時における注意点 内部回路の簡単な設計 選定方法 とは など

在plc电器控制中简单回路图的梯形图和实际接线图比较

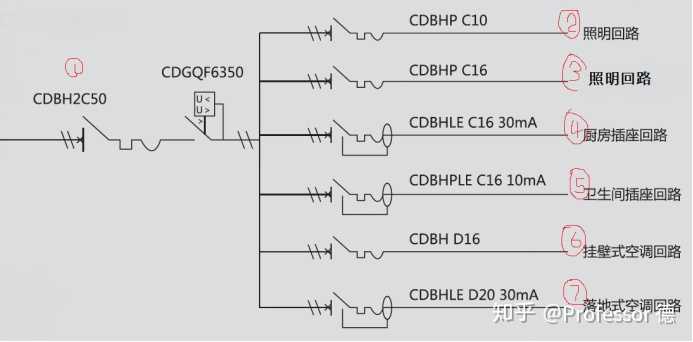

家用回路开关接线图 第1页 一起扣扣网

Adalm00實驗 運算放大器作為比較器 Compotech Asia

打卡第3天 電氣二次迴路 三相斷路器控制迴路圖分析 每日頭條

nビット比較回路

電壓比較器 電壓比較器是對輸入信號進行鑑別與比較的電路 是組成非正弦波發 華人百科

有极性电解电容并联电路 Pcb抄板 Pcb打样 深圳市亿品优高精密电子有限公司官网

回路合成

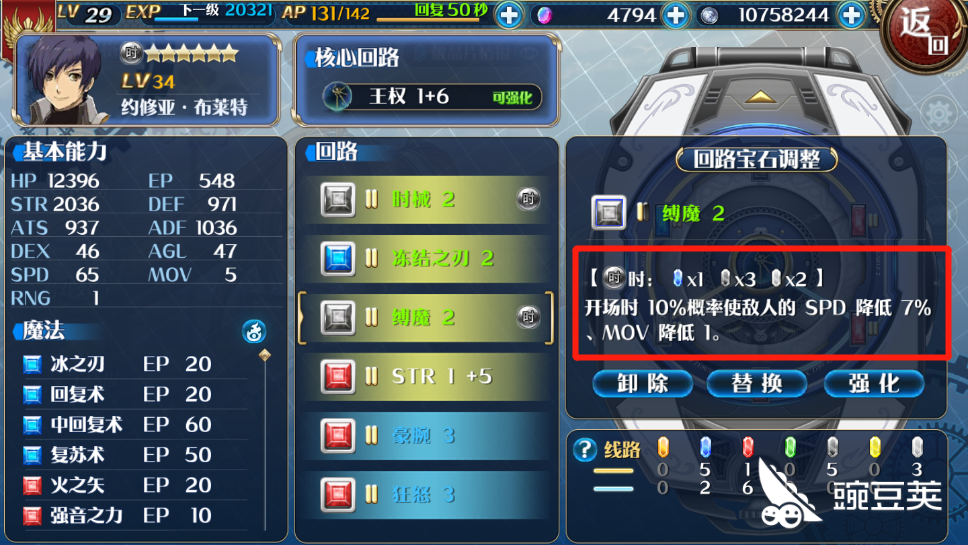

星之轨迹高级回路怎么获得 高级回路原来这么简单 豌豆荚

コンピュータの仕組み 基本論理回路 機械語 Yokkunsの日記

Circuit Explanation For Ultrasonic Range Meter

别墅强电箱 如果分回路用2p漏电开关30ma 总开关也2p带漏电30ma 发生漏电之后 知乎

典型迟滞比较器电路图大全 四款典型迟滞比较器电路设计原理图详解 电子发烧友网

交流发电机励磁电压太低是什么问题 如何解决 交流发电机与直流发电机 电工基础 电工屋

02 号 大小比較回路 Astamuse

三极管的三种放大电路解析 放大电路的三种组态比较 电子发烧友网

简单了解滤波 稳压 比较 运放电路 用户体验 Rohm技术社区

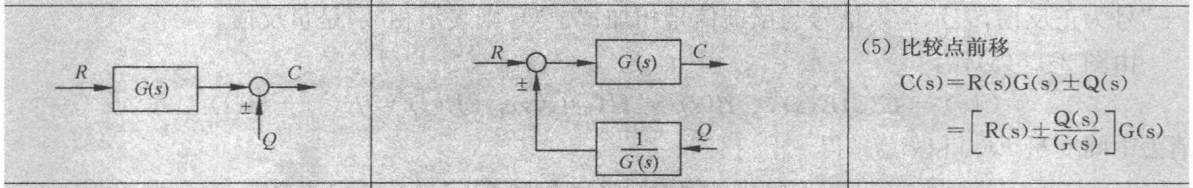

自动控制原理结构图等效规则 早做准备

論理ゲート ナノエレクトロニクス

正反转控制回路以及正反转电路的常见故障 电工之家手机版

最新消息 得邁斯科技 Fluke校正器入口網站 Fluke Ametek Ircon Ca 溫度校正 壓力校正 電量校正 程控校正 迴路校正 紅外線溫度計 熱像儀 雷射修阻機

從四個方面談llc變壓器設計經驗 教你如何舉一反三 電子發燒友網 微文庫

节流回路图 第1页 一起扣扣网

实验课程 西安交通大学核安全与运行研究室 Nuclear Safety And Operation Lab Nusol

Woa1 位相比較装置およびdll回路 Google Patents

用了plc 就告別繼電器了 每日頭條

液压顺序动作回路的三种典型控制 动图 看点快报

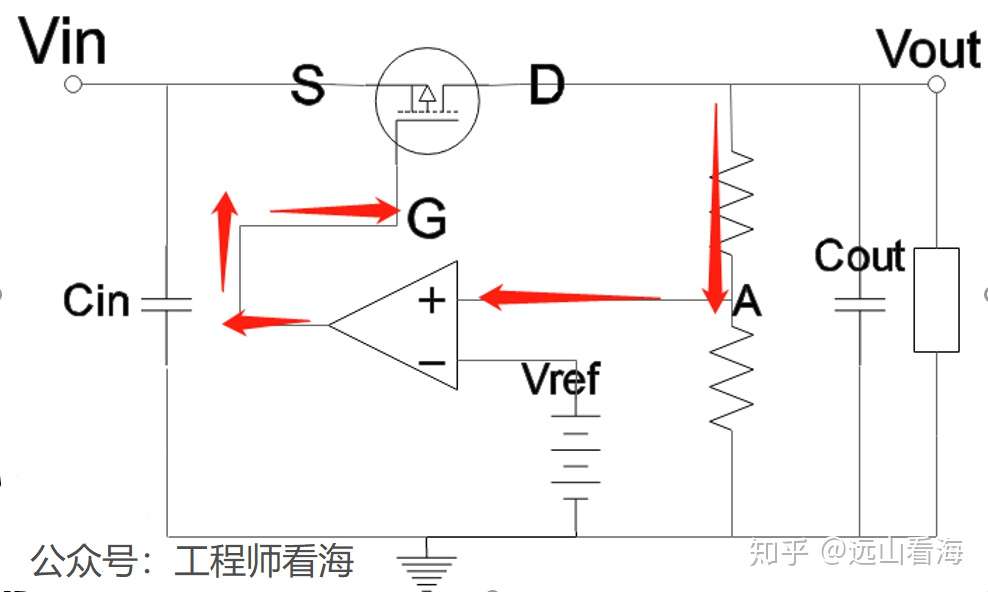

电源系列1 Ldo原理介绍 一 知乎

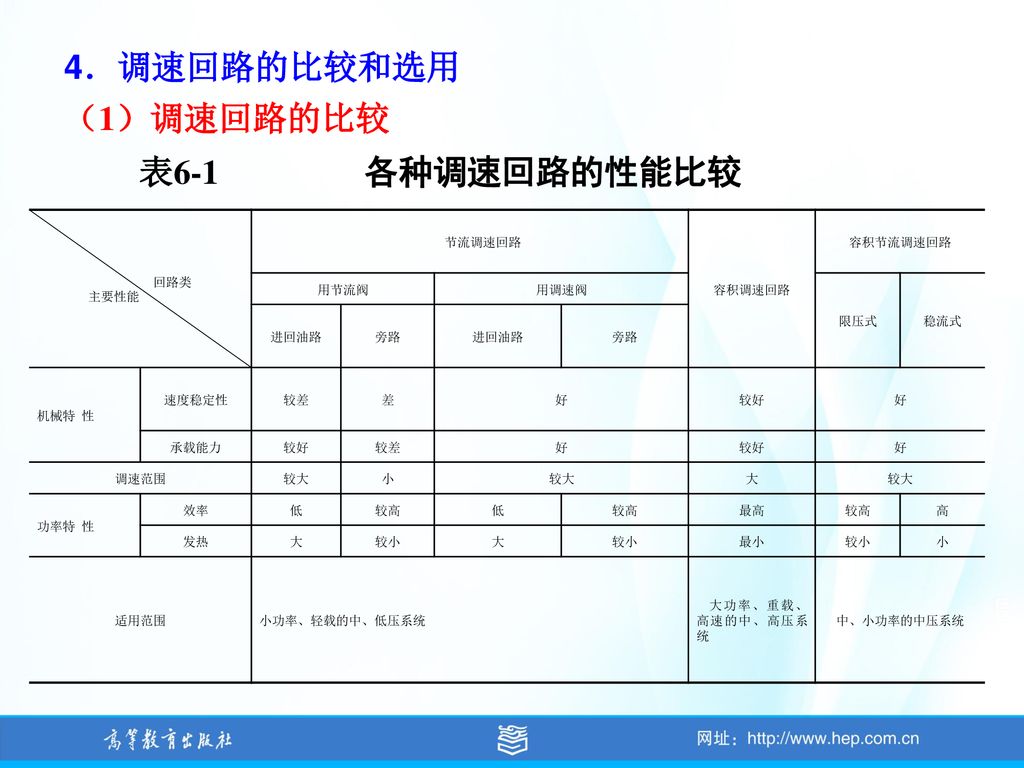

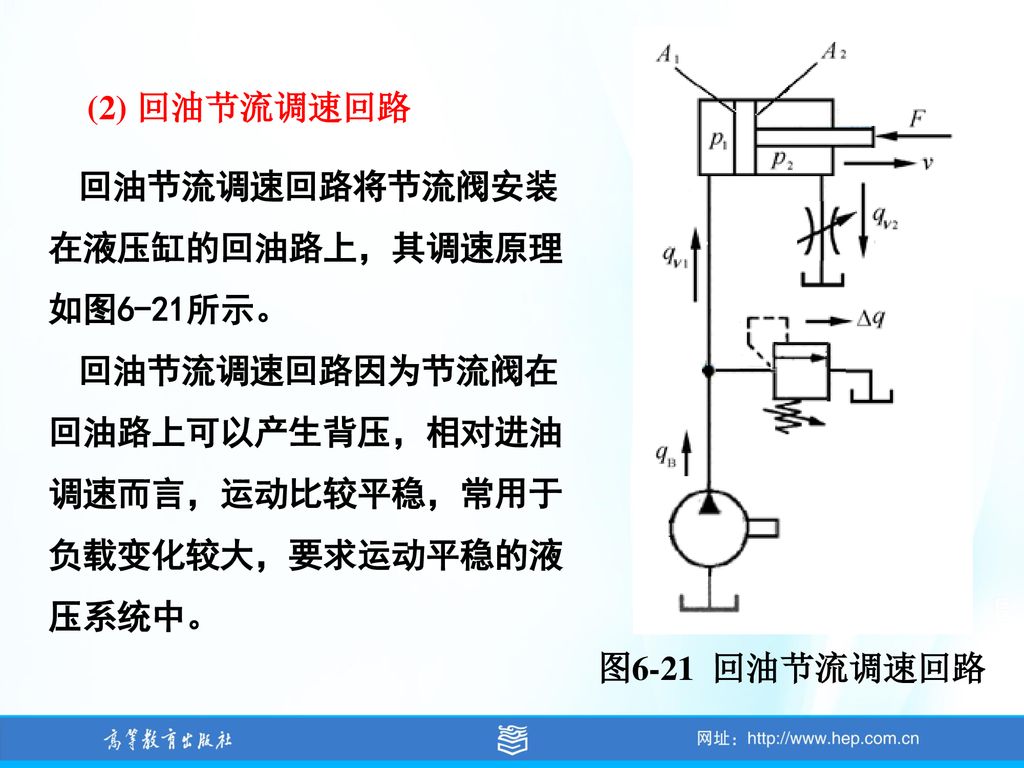

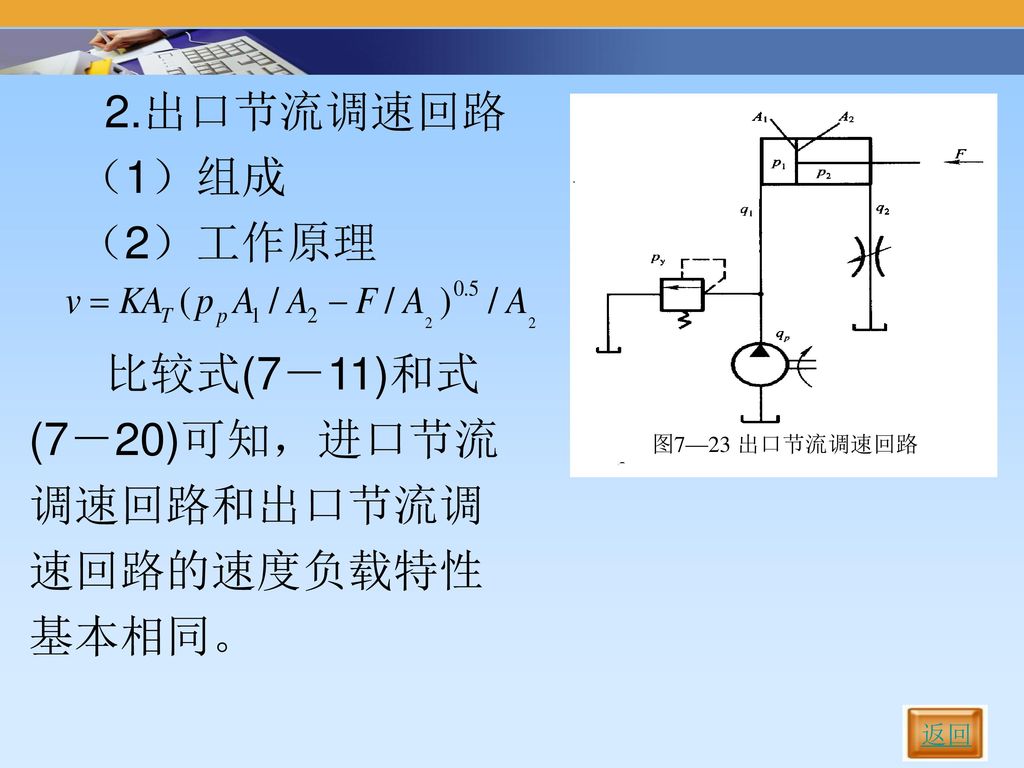

第六章液压系统的基本回路 Ppt Download

什么是闭式回路液压系统用在哪些设备上

施密特觸發器 維基百科 自由的百科全書

1999 号 比較回路 Astamuse

家用電路中 設計多少個迴路比較合適 壹讀

电源转换应用中数字反馈回路的益处 电子工程世界 Eeworld

继电保护及二次回路 学习 百度文库

过流自锁电路图解析 电子发烧友网

第六章液压系统的基本回路 Ppt Download

コンパレータ 比較器 電子工作で覚える 電子回路

Lc串 并联谐振回路 Chenyx的博客 Csdn博客

電流輸出型dac 的精確傳感器控制 Digikey

傳統閉迴路控制系統控制器致動器 馬達 過程 手臂 感測器設定點受控結果誤差比較器 Ppt Katebasma

在plc电器控制中简单回路图的梯形图和实际接线图比较

Index Of Rde Contents Course Mechatronics Fig

继电器 智汇三农

家装电线回路如何划分才合理 诸暨网

Tq 100型同期继电器 上海约瑟电器有限公司

节流回路图 第1页 一起扣扣网

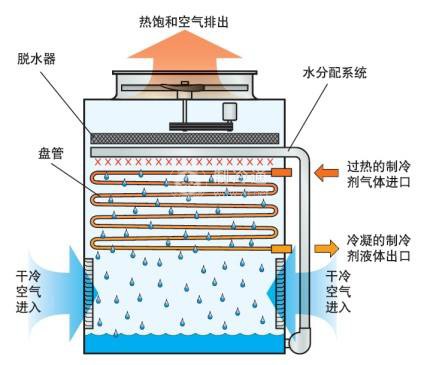

冷库建造中蒸发式冷凝器的控制回路 工程技术 制冷资讯

第7章液压基本回路方向控制回路7 1 7 2 压力控制回路速度控制回路7 3 多缸工作控制回路7 4 Ppt Download

Pid控制器 维基百科 自由的百科全书

別再說龜毛啦 處女座隻是大腦回路比較復雜 維爾戈星座大揭秘

電氣二次迴路圖學習有哪些竅門 雪花新闻

双回路开关接线实物图 搜狗图片搜索

最高のマインクラフト 驚くばかり比較 回路

左家庄信息港

晶体管放大电路三种组态的比较 腾讯视频

一文搞懂因果回路图 掌握系统思考关键工具 管理人网 中国第一企业管理资源中心

Circuit Explanation Of The Temperature Controller Of The Bending Apparatus

沈浸在音樂之中 貓窩工坊drc Do Something Rca訊號線ground Loop

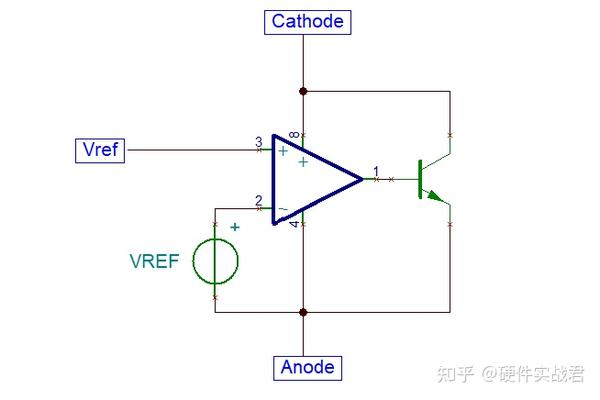

如何使用tl431搭建恒流电路 知乎

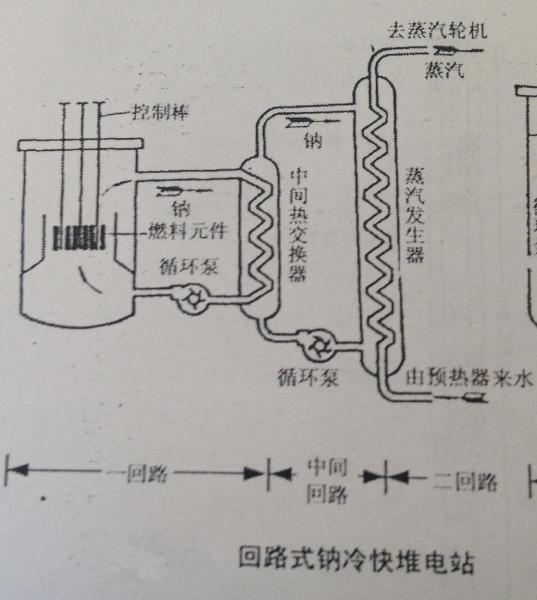

快中子堆 搜狗百科

1998 号 電流比較回路 Astamuse

一文搞懂因果回路图 掌握系统思考关键工具 安晓辉生涯 微信公众号文章阅读 Wemp

0 件のコメント:

コメントを投稿